- ผู้เขียน Lynn Donovan donovan@answers-technology.com.

- Public 2023-12-15 23:54.

- แก้ไขล่าสุด 2025-01-22 17:42.

VHDL และ Verilog ถือเป็นภาษาการออกแบบดิจิทัลเอนกประสงค์ ในขณะที่ SystemVerilog แสดงถึงเวอร์ชันปรับปรุงของ Verilog . VHDL มีราก ใน ภาษาโปรแกรม Ada ทั้งในแนวคิดและไวยากรณ์ในขณะที่ Verilog's สามารถติดตามรากกลับไปเป็น HDL รุ่นแรกที่เรียกว่า Hilo และภาษาการเขียนโปรแกรม C

ผู้คนยังถามว่า VHDL หรือ Verilog ไหนดีกว่ากัน?

VHDL ละเอียดกว่า Verilog และ itis ก็ยังมีไวยากรณ์ที่ไม่ใช่ C เช่น กับ VHDL คุณมีโอกาสเขียนโค้ดมากขึ้น Verilog มี ดีกว่า เข้าใจเกี่ยวกับการสร้างแบบจำลองฮาร์ดแวร์ แต่มีโครงสร้างการเขียนโปรแกรมในระดับที่ต่ำกว่า Verilog ไม่ละเอียดเท่า VHDL จึงมีขนาดกะทัดรัดกว่า

นอกจากนี้ Verilog มีประโยชน์อย่างไร? Verilog เป็นภาษาคำอธิบายฮาร์ดแวร์ atextual format สำหรับอธิบายวงจรไฟฟ้าและระบบต่างๆ ที่ใช้กับการออกแบบทางอิเล็กทรอนิกส์ Verilog มีวัตถุประสงค์เพื่อใช้ในการตรวจสอบผ่านการจำลอง สำหรับการวิเคราะห์เวลา สำหรับการทดสอบ (การวิเคราะห์ความสามารถในการทดสอบและการจัดลำดับข้อบกพร่อง) และสำหรับการสังเคราะห์ทางตรรกะ

ในลักษณะนี้ Verilog และ SystemVerilog แตกต่างกันอย่างไร

หลัก ความแตกต่างระหว่าง Verilog และ SystemVerilog คือว่า Verilog เป็นฮาร์ดแวร์ DescriptionLanguage ในขณะที่ SystemVerilog เป็นคำอธิบายฮาร์ดแวร์และภาษาการตรวจสอบฮาร์ดแวร์ตาม Verilog . กล่าวโดยย่อว่า SystemVerilog เป็นเวอร์ชันปรับปรุงของ Verilog พร้อมคุณสมบัติเพิ่มเติม

VHDL ใน VLSI คืออะไร?

VLSI ออกแบบ - VHDL บทนำ.โฆษณา. VHDL ย่อมาจากภาษาคำอธิบายฮาร์ดแวร์วงจรรวมความเร็วสูงมาก เป็นภาษาโปรแกรมที่ใช้ในการสร้างแบบจำลองระบบดิจิทัลโดยกระแสข้อมูล รูปแบบพฤติกรรมและโครงสร้างของการสร้างแบบจำลอง

แนะนำ:

ความแตกต่างระหว่าง AVR และ ARM คืออะไร?

ดังนั้นหากคุณต้องการเปรียบเทียบ Arduinos กับ AVR (Uno, Nano, Leonardo) และ Arduinos ที่มี ARMs (Due, Zero, Teensy) ความแตกต่างใหญ่ที่ AVR เป็นสถาปัตยกรรม 8 บิต และ ARM เป็นสถาปัตยกรรมแบบ 32 บิต

ความแตกต่างระหว่าง PreparedStatement และ CallableStatement คืออะไร?

CallableStatement ใช้เพื่อดำเนินการขั้นตอนการจัดเก็บ CallableStatement ขยาย PreparedStatement คือ IN – ใช้เพื่อส่งผ่านค่าไปยังกระบวนงานที่เก็บไว้, OUT – ใช้เพื่อเก็บผลลัพธ์ที่ส่งคืนโดยกระบวนงานที่เก็บไว้ และ IN OUT – ทำหน้าที่เป็นทั้งพารามิเตอร์ IN และ OUT

ความแตกต่างระหว่าง lexical และ syntax analyzer คืออะไร?

ความแตกต่างหลัก ระหว่างการวิเคราะห์คำศัพท์และการวิเคราะห์ไวยากรณ์คือ การวิเคราะห์คำศัพท์จะอ่านซอร์สโค้ดทีละอักขระและแปลงเป็น lexemes ที่มีความหมาย (โทเค็น) ในขณะที่การวิเคราะห์ไวยากรณ์ใช้โทเค็นเหล่านั้นและสร้างแผนผังแยกเป็นเอาต์พุต

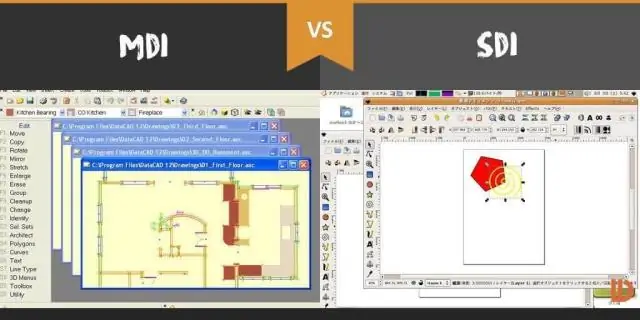

ความแตกต่างระหว่าง MDI และ SDI คืออะไร?

Multiple Document Interface (MDI): MDI ให้คุณเปิดเอกสารมากกว่าหนึ่งฉบับพร้อมกัน TheMDI มีหน้าต่างหลัก และหน้าต่างย่อยจำนวนเท่าใดก็ได้ Single Document Interface (SDI): SDI เปิดแต่ละเอกสารในหน้าต่างหลักของตัวเอง แต่ละหน้าต่างจะมีเมนู แถบเครื่องมือ และรายการในแถบงานของตัวเอง

ความแตกต่างระหว่าง Avamar และ NetWorker คืออะไร?

Avamar นั้นรวดเร็ว มีประสิทธิภาพในการสำรองและกู้คืนข้อมูลผ่านซอฟต์แวร์และฮาร์ดแวร์ที่สมบูรณ์ ซอฟต์แวร์สำรองข้อมูลและกู้คืน EMC NetWorker จะรวมศูนย์ ทำให้เป็นอัตโนมัติ และเร่งการสำรองและกู้คืนข้อมูลในสภาพแวดล้อมไอทีของคุณ